5.3. Логический элемент с тремя состояниями

Схема логического элемента

с тремя состояниями заимствована из монографии [8] и несколько модифицирована

с учетом возможностей программы EWB. За основу взят базовый элемент серии 134

и к нему добавлен элемент, обеспечивающий возможность реализации режима третьего

состояния или так называемого Z-состоя-ния. Следует отметить, что рассматриваемый

элемент является важным компонентом многих цифровых ИМС, начиная от простейших

логических элементов (например, К155ЛА9) и кончая сложными регистрами и шинными

формирователями, обеспечивающими возможность реализации наиболее распространенных

архитектур ЭВМ и микропроцессорных систем управления с общей шиной.

Принципиальная схема логического

элемента с тремя состояниями представлена на рис. 9.15. Она содержит базовый

логический элемент серии 134 на транзисторах VT1…VT4, резисторах R1…R4 и

диоде VD2. В базовом элементе в качестве VT1 используется так называемый многоэмиттерный

транзистор, однако ввиду отсутствия такового в библиотеке EWB он представлен

обычным транзистором. Ко входу In логического элемента подключен имитатор входного

сигнала на переключателе D, управляемый с клавиатуры клавишей D, резистора Rd,

имитирующего выходное сопротивление источника логического нуля, и источника

напряжения V=+5 В с внутренним сопротивлением 1 кОм, имитирующего источник входного

сигнала в режиме генерации логической единицы. К точке А схемы подключены диод

VD1 в имитатор источника управления состоянием выхода логического элемента на

переключателе Е, управляемого клавишей Е. Все элементы дополнительной схемы

— компоненты из библиотек Passive и Control. В исходном состоянии диод VD1 закрыт

напряжением положительной полярности на его катоде и он не оказывает влияния

на работу схемы. К эмиттеру транзистора VT1 подключен резистор Rd, на котором

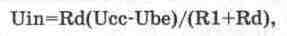

создается падение напряжения  (9.1)

(9.1)

где Uсс=5В — напряжение

питания; Ube=0,7 В — напряжение база-эмиттер открытого транзистора.

При

(9.2)

(9.2)

логический элемент воспринимает

входной сигнал как сигнал логического нуля. При этом напряжение на коллекторе

транзистора VT1 и базе VT2 недостаточно для открывания последнего. В результате

падение напряжения на резисторе R3 близко к нулю и транзистор VT4 будет закрыт,

а база транзистора VT3 соединена с источником питания Ucc через резистор R2

и VT3 будет открыт. При этом выходное напряжение Uy, измеряемое мультиметром,

примерно равно  (9.3)

(9.3)

где Uкбнас<1 В — напряжение

насыщения транзистора VT4; Uпp<l В — падение напряжения на диоде VD2; Ry

— сопротивление нагрузки, равное в данном случае входному сопротивлению мультиметра.

Если выбрать Ry>>R4,

то Uy>3 В, т.е. при подаче на вход сигнала логического нуля на выходе получим

сигнал логической единицы. Таким образом, схема на рис. 9.15 является логическим

элементом НЕ (инвертором).

При переводе клавишей D

одноименного переключателя в другое положение на эмиттер транзистора VT1 подается

сигнал логической единицы, в результате чего эмиттерный переход закрывается,

и транзистор VT1 переводится в инверсный режим. В этом случае под действием

тока, протекающего по цепи база-коллектор VT1, транзистор VT2 открывается и

за счет падения напряжения на резисторах R2, R3 транзистор VT3 закроется, а

VT4 — откроется, и на выходе Y установится сигнал логического нуля.

При переводе клавишей Е

одноименного переключателя во второе положение напряжение коллектора транзистора

VT2 (точка А) будет равно  (9.4)

(9.4)

При выполнении неравенства

R2>>Rd напряжение Uпp<l В, что недостаточно для открытия двух переходов

(эмиттерного и диодного), и транзистор VT3 будет закрыт вне зависимости от состояния

транзистора VT2. Если этот транзистор открыт (наихудший случай), то с учетом

его напряжения насыщения, сравнимого с U„p, падение напряжения на резисторе

R3 будет ничтожно малым, следовательно, транзистор VT4 будет закрыт. Таким образом,

выход схемы полностью отключается от нагрузки, что может быть зафиксировано

мультиметром в режиме омметра — он будет измерять очень большое сопротивление.

Кроме демонстрации рассмотренных

режимов схемы, она может быть использована также для исследования:

О помехоустойчивости по

основному входу и входу разрешения третьего состояния путем варьирования сопротивления

Rd с учетом выражений (9.1), (9.2) и (9.4);

О влияния сопротивления

нагрузки на амплитуду выходного напряжения вентиля при формировании сигнала

логической единицы путем изменения входного сопротивления мультиметра с учетом

выражения (9.3);

О влияния сопротивления

нагрузки, подключенной между выходом и шиной питания Ucc, на выходное напряжение

вентиля при формировании сигнала логического нуля;

О влияния емкостной нагрузки

на форму и амплитуду выходного сигнала вентиля;

в этом случае к выходу

необходимо подключить конденсатор переменной емкости и осциллограф, а для генерации

прямоугольных сигналов необходимо удерживать клавишу D, при этом частота следования

импульсов будет равна частоте повторения символов для данной клавиатуры;

О аналогичного элемента

с тремя состояниями в более быстродействующей серии 155, для чего сопротивления

всех резисторов необходимо уменьшить в 10 раз.

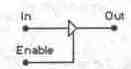

Заметим, что в составе

библиотеки компонентов имеется неинвертирующий элемент с тремя состояниями.

Он показан на рис. 9.16, где обозначено: In, Out, Enable — вход, выход и вход

сигнала разрешения. При подаче логического нуля на вход разрешения выход буфера

переводится в третье состояние.

Рис. 9.16.

Буферный элемент с тремя состояниями

В заключение упомянем о

логическом элементе с открытым коллектором. Его схема отличается от рис. 9.15

тем, что в ней отсутствует транзистор VT3, а коллектор транзистора VT4 подключен

к одному из внешних выводов. На этот вывод через резистор нагрузки подается

напряжение питания, которое может превосходить напряжение питания всей ИМС.

Контрольные вопросы и задания

1. Какими замечательными

свойствами обладает логический элемент с тремя состояниями, какие задачи цифровой

техники он позволил решить?

2. Проведите исследования

логического элемента на рис. 9.15 в соответствии с приведенными в конце раздела

рекомендациями.

|